#### The Microarchitecture Level

Chapter 4

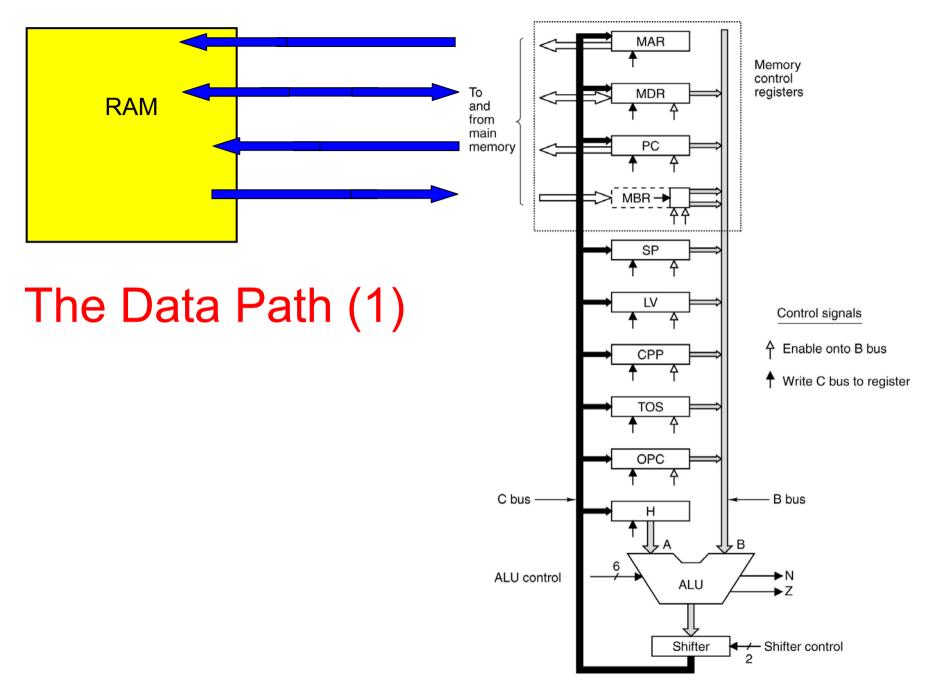

# The Data Path (2)

| F <sub>o</sub> | F <sub>1</sub> | ENA | ENB | INVA | INC | Function  |

|----------------|----------------|-----|-----|------|-----|-----------|

| 0              | 1              | 1   | 0   | 0    | 0   | Α         |

| 0              | 1              | 0   | 1   | 0    | 0   | В         |

| 0              | 1              | 1   | 0   | 1    | 0   | Ā         |

| 1              | 0              | 1   | 1   | 0    | 0   | B         |

| 1              | 1              | 1   | 1   | 0    | 0   | A + B     |

| 1              | 1              | 1   | 1   | 0    | 1   | A + B + 1 |

| 1              | 1              | 1   | 0   | 0    | 1   | A + 1     |

| 1              | 1              | 0   | 1   | 0    | 1   | B + 1     |

| 1              | 1              | 1   | 1   | 1    | 1   | B – A     |

| 1              | 1              | 0   | 1   | 1    | 0   | B – 1     |

| 1              | 1              | 1   | 0   | 1    | 1   | -A        |

| 0              | 0              | 1   | 1   | 0    | 0   | A AND B   |

| 0              | 1              | 1   | 1   | 0    | 0   | A OR B    |

| 0              | 1              | 0   | 0   | 0    | 0   | 0         |

| 1              | 1              | 0   | 0   | 0    | 1   | 1         |

| 1              | 1              | 0   | 0   | 1    | 0   | <b>-1</b> |

Useful combinations of ALU signals and the function performed.

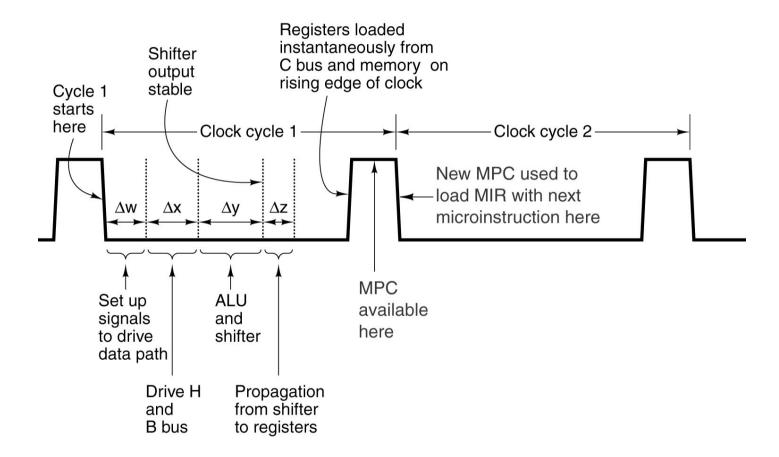

## **Data Path Timing**

Timing diagram of one data path cycle.

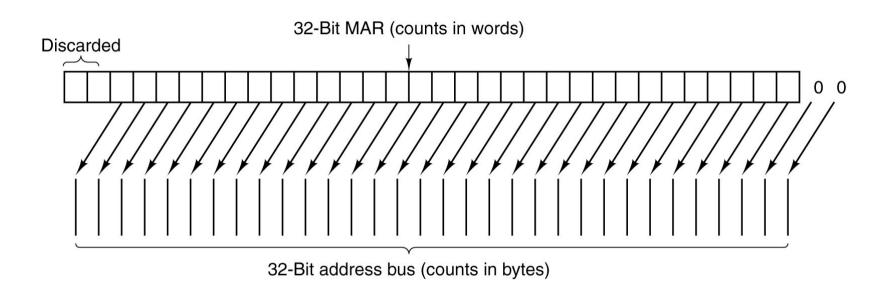

## **Memory Operation**

Mapping of the bits in MAR to the address bus.

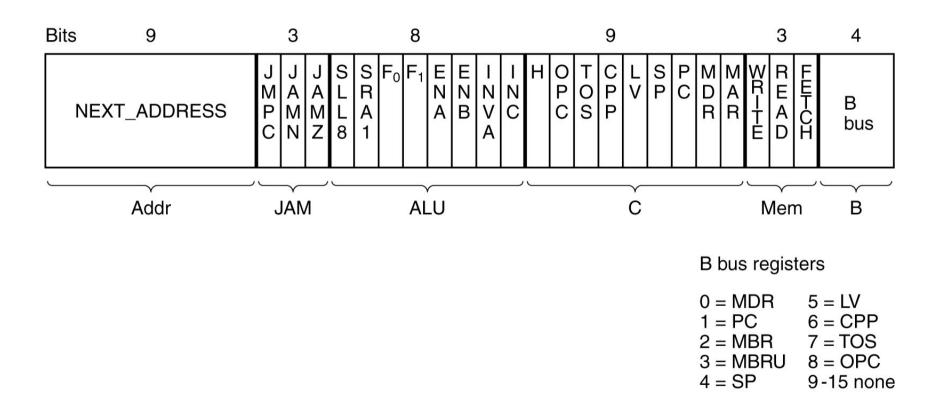

#### **Microinstructions**

The microinstruction format for the Mic-1.

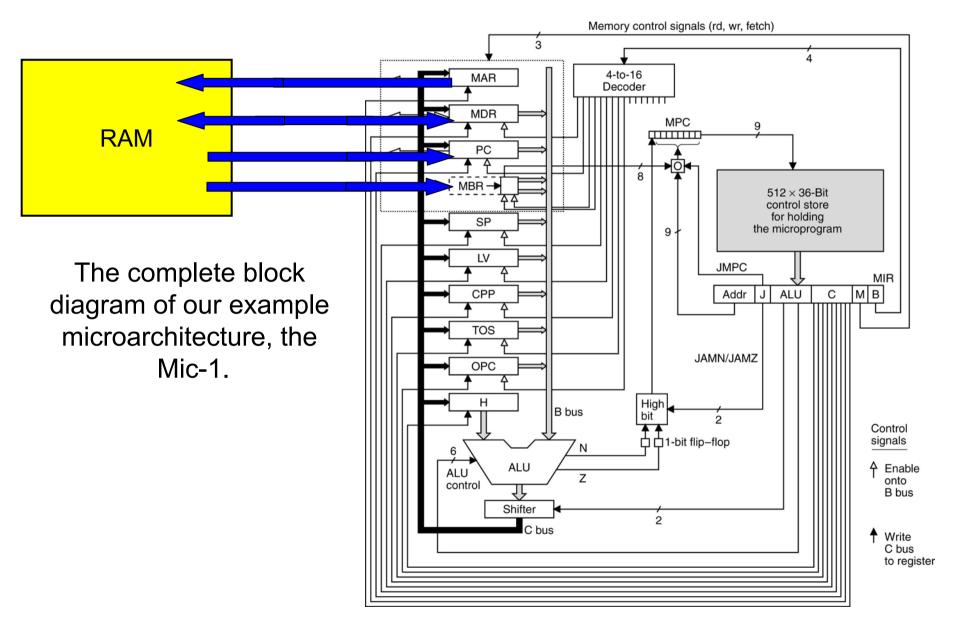

### Microinstruction Control: The Mic-1 (1)

### Microinstruction Control: The Mic-1 (2)

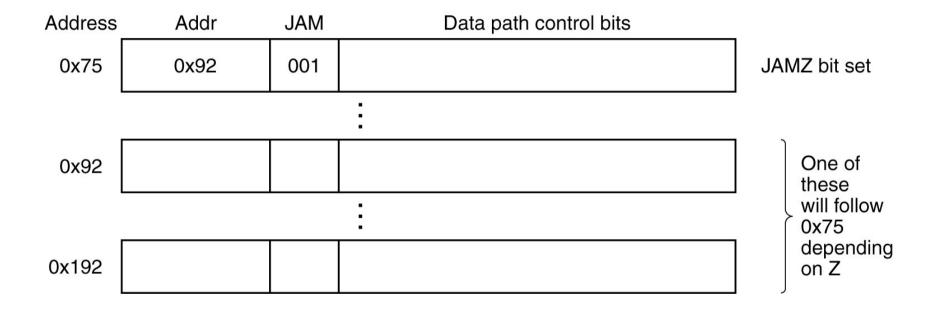

A microinstruction with JAMZ set to 1 has two potential successors.